VHDL expert with board

$10-30 USD

ปิดแล้ว

โพสต์ ประมาณ 7 ปีที่ผ่านมา

$10-30 USD

ชำระเงินเมื่อส่งงาน

I can send all the details upon request.. looking for VHDL expert to handle a task

sign meets the specifications; d) report about your design.

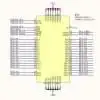

You are required to design code for your target hardware (a Digilent Basys3 board with a Xilinx

Artix 7 FPGA) in order to implement a design that meets the specifications (below). You are

required to submit working and correct code and you are strongly encouraged to use a modular

coding style (allowing for greater flexibility, maintainability, modularity, and reusability). To show

that you master all aspects of the language, your code should prevalently use concurrent statements

for combinatorial circuits and sequential code for sequential circuits. Additionally, the use of nonstandard

packages (e.g. STD_LOGIC_ARITH, STD_LOGIC_UNSIGNED, STD_LOGIC_SIGNED) and BUFFER

ports is forbidden, while the use of INOUT ports is accepted only when strictly necessary

รหัสโปรเจกต์: 13203980

เกี่ยวกับโปรเจกต์

8 ข้อเสนอ

โปรเจกต์ระยะไกล

ใช้งานอยู่ 7 ปีที่ผ่านมา

กำลังมองหาการสร้างรายได้ใช่ไหม?

ประโยชน์ของการประมูลกับ Freelancer

กำหนดงบประมาณและกรอบเวลาของคุณ

รับเงินจากการงานของคุณ

อธิบายข้อเสนอของคุณในภาพรวม

ลงทะเบียนและเสนอราคาฟรี

เกี่ยวกับลูกค้า

Mutrah, Oman

359

ยืนยันวิธีการชำระเงินแล้ว

เป็นสมาชิกตั้งแต่ พ.ย. 17, 2009

การยืนยันลูกค้า

งานอื่นๆ จากลูกค้ารายนี้

$2-8 USD / hour

$10-30 USD

$10-30 USD

$2-8 USD / hour

$30-250 USD

งานที่คล้ายกัน

$190 NZD

₹12500-37500 INR

£250-750 GBP

min €36 EUR / hour

$250-750 USD

$30-250 USD

$30-250 USD

$30-250 USD

₹750-1250 INR / hour

$25-50 USD / hour

$10-30 CAD

$400-450 USD

$10-60 USD

$190 NZD

£10-20 GBP

$100 USD

₹600-1500 INR

$30-250 USD

$10-30 CAD

$10-30 CAD

ขอบคุณ! เราได้ส่งลิงก์สำหรับเครดิตฟรีให้คุณทางอีเมลแล้ว

เกิดข้อผิดพลาดขณะส่งอีเมลของคุณ กรุณาลองอีกครั้ง

กำลังโหลดตัวอย่าง

ได้รับอนุญาตสำหรับตำแหน่งทางภูมิศาสตร์

เซสชั่นการเข้าสู่ระบบของคุณหมดอายุและคุณได้ออกจากระบบแล้ว กรุณาเข้าสู่ระบบอีกครั้ง